#### **IOWA STATE UNIVERSITY Digital Repository**

Retrospective Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

1968

# Automatic allocation of digital computer storage resources for time-sharing

Frank Gerald Soltis Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/rtd

Part of the <u>Electrical and Electronics Commons</u>

#### Recommended Citation

Soltis, Frank Gerald, "Automatic allocation of digital computer storage resources for time-sharing" (1968). Retrospective Theses and Dissertations. 4633.

https://lib.dr.iastate.edu/rtd/4633

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

### This dissertation has been microfilmed exactly as received

69-9896

SOLTIS, Frank Gerald, 1940-AUTOMATIC ALLOCATION OF DIGITAL COM-PUTER STORAGE RESOURCES FOR TIME-SHARING.

Iowa State University, Ph.D., 1968 Engineering, electrical

University Microfilms, Inc., Ann Arbor, Michigan

## AUTOMATIC ALLOCATION OF DIGITAL COMPUTER STORAGE RESOURCES FOR TIME-SHARING

bу

#### Frank Gerald Soltis

A Dissertation Submitted to the

Graduate Faculty in Partial Fulfillment of

The Requirements for the Degree of

DOCTOR OF PHILOSOPHY

Major Subject: Electrical Engineering

#### Approved:

Signature was redacted for privacy.

In Charge of Major Work

Signature was redacted for privacy.

Head of Major Department

Signature was redacted for privacy.

Dean of Graduate College

Iowa State University Ames, Iowa

1968

#### TABLE OF CONTENTS

|                                                    | Page |

|----------------------------------------------------|------|

| INTRODUCTION                                       | 1    |

| ANALYSIS OF TIME-SHARING COMPUTER SYSTEMS          | 5    |

| Mathematical Analysis                              | 5    |

| Simulation                                         | 7    |

| Selection of an Analysis Technique                 | 8    |

| A Description of the Simulation Program            | 10   |

| SELECTION OF A TEST CASE                           | 17   |

| Equipment Configuration                            | 18   |

| Job Mix Selection                                  | 20   |

| PAGING STRUCTURE OF A TIME-SHARING COMPUTER SYSTEM | 35   |

| Demand Paging                                      | 35   |

| Drum Paging Structure                              | 37   |

| IMPROVEMENT OF SYSTEM PERFORMANCE                  | 43   |

| Scheduling of the Paging Drums                     | 47   |

| Multiple Sets of Registers                         | 48   |

| Hardware Paging Structure                          | 50   |

| Queue Structures                                   | 67   |

| EVALUATIONS AND CONCLUSIONS                        | 73   |

| Evaluation of System Performance                   | 73   |

| Conclusions                                        | 81   |

| Concluding Remarks                                 | 83   |

| BIBLIOGRAPHY                                       | 85   |

| ACKNOWLEDGMENTS                                    | 87   |

| APPENDIX                                           | 88   |

#### INTRODUCTION

"Time-sharing" is the term used to describe a computer system in which each user in turn is given a certain amount of operating time (i.e., a time slice). In this way the system's resources can be effectively "shared" among many users. Most of the current time-sharing systems operate in a multiprogramming environment, wherein a number of programs reside in main core at the same time. A problem which soon becomes apparent is that, for a large number of users and large programs, not all programs can fit into main core at the same time. The solution to this problem is to provide the system with a large capacity auxiliary storage device (i.e., secondary storage) which may be considerably slower than main core but which is able to efficiently transfer blocks of information to and from main core. These blocks of information are called "pages".

The concept of paging was first introduced on the ATLAS computer, which is described in a paper by Kilburn et al. (8). Paging can be defined as the transmission to and from secondary storage, the relocation, and the execution of programs on a paged basis. Relocation refers to the translation of a program's addresses into the actual locations in main core. This is needed because it is not possible to put a page into the same main core location every time it is read in. Whenever a program refers to some address which is not in main core, it is necessary for the system to locate the page in secondary storage which contains that address and read in that page. It may be necessary to write out to secondary storage some page in main core in order to make room for the page being read in. Thus, pages are constantly being transferred to and from

secondary storage in a paged time-sharing computer system.

Since the paging structure is unique to a time-sharing system, a number of design decisions have been encountered which are not present in the design of a conventional computer system. The selection and organization of secondary storage; the means of accomplishing the relocation operation; the development of algorithms for page replacement, page reading, and page writing; and numerous other decisions must be made in order to design the paging structure.

Because of the large number and complexity of these many design decisions, it is not surprising that many different paging structures for time-sharing systems have been proposed. The performance of some of these proposed structures has been very good; others have not fared as well. The causes of the poor system performance of some systems and remedies for this poor performance have generated a great deal of interest among system designers. While it is obvious that the many design decisions do affect the performance of the time-sharing system, very little is known about how much of an effect any particular decision has on the total system performance.

This study will examine the behavior of a paged time-sharing system with the objective of determining those areas of the paging structure which offer the most opportunity for improvements in system performance. Because there is no universally accepted design for a paging structure, it will be necessary to select some particular system whose design is representative of current time-sharing philosophy and to analyze this system thoroughly. Modifications to the paging structure which improve the total system performance will be proposed and the generalized results

found for this system will be extended to other systems.

Some means must be found to analyze the operation of a time-sharing system. The second chapter describes some of the analysis techniques which have previously been developed. The system selected to be studied and a description of the analysis technique chosen are also presented in this chapter.

In order to provide valid results for the system study, very careful consideration must be given to the selection of a test case. The determination of the test cases and the reasons behind their selection are given in the third chapter.

In the fourth chapter the effect of the paging devices on system performance is examined. The paging drums are shown to be able to deliver pages to the system at a rate which can maintain satisfactory system performance. Some of the major causes of poor system performance are pointed out in this chapter.

Those areas of the paging structure which degrade the system performance are studied in the fifth chapter. The proposed changes to these areas are given in detail and the effects of each change on the system behavior are presented. Each change is carefully examined on its own merits to determine how significant an improvement in system performance can be obtained.

The sixth chapter summarizes the results which have been obtained by modifications to the paging structure. These results are then generalized to determine which areas of the paging structure can offer the most opportunity for improvements in system performance. Additional areas for

study are proposed and some concluding comments about time-sharing studies are given.

\_\_\_

#### ANALYSIS OF TIME-SHARING COMPUTER SYSTEMS

This chapter is concerned with the selection of an analysis technique which can be used to investigate the operation of a time-sharing computer system. A survey of some of the studies that have been made is first presented, followed by a more detailed description of the technique selected. Basically, there are two meens of analyzing the behavior of a time-sharing system: mathematical analysis and simulation.

#### Mathematical Analysis

In order to develop a mathematical model of a system, some structure must be assumed. A common model of a time-sharing system is taken to be an interconnection of queues and processes with a known stochastic flow of tasks between them. An arithmetic processor, a stored program, a data channel, and even a user are considered to be processes. On the other hand, a queue is regarded as a list of uncompleted tasks whose routes between processes are indistinguishable. Associated with each process is a service time, representing the length of time a task will occupy that process. Other factors affecting the flow between processes, such as arrival times, priority assignments, etc., must also be represented in the model. The state of the system at any time is described by the number of entries in the various queues.

The structure assumed is a fairly good representation of general purpose, time-sharing system and is the model derived from a Markov chain. Taken together with the assumed probability distributions for arrival and service times, this model can be analyzed by means of Markov process theory to predict system behavior. The objective of the analysis is to evaluate

the probability distributions of the states. Once these distributions are known, other probablistic measures of interest, such queue lengths, processor utilization times, and through-put rates, can be determined. For a discussion of how these distributions are obtained for a Markov model, see the paper by Wallace and Rosenberg (18).

There have been many studies conducted to analyze computer systems using Markov models. One of the best studies was made by Smith (17). In his paper Smith describes a paged, time-sharing structure for which a queuing model was derived. The model did represent the system operations fairly well, but the requirement that the model remain a Markov process severely restricted its flexibility. However, this is one of the few studies which have attempted to analyze a paged structure.

Not all analyses concern themselves with the performance of the entire system. A paper by Fife (2) describes a study of job scheduling techniques used in a time-sharing system. Krishnamoorthi and Wood (9) explored methods which would aid in the selections of time slice intervals.

The papers described above, as well as many others, represent attempts to analyze a general purpose, time-sharing system using mathematical techniques. While none of them have completely achieved this goal, a number of them have made significant contributions. All suffer from a general lack of flexibility. Unfortunately, the assumptions made by many in proposing models, render their results totally useless for any practical system.

#### Simulation

The second means of analyzing the performance of time-sharing computer systems is simulation. An excellent review of computer system simulations is given in a paper by Huesmann and Goldberg (6). Some of the more important simulation studies are discussed in the following paragraphs.

Scherr (16) developed a very good simulation of the MAC system at MIT. The description of the system is through a series of statements and subroutines written in MAD (Michigan Algorithm Decoder) which allow the hardware configuration and operating system to be specified in as much or as little detail as desired. The job mix is generated according to desired statistics which are inputs to the simulator. The program also uses statistics gathering routines to obtain data on the job mix which outputs along with response times, through-put rates, queue lengths, overhead times, etc.

Fine and McIsaac (4) discuss a simulation of the System Development Corporation (SDC) Q-32 time-sharing system. Most of the important characteristics of the simulation, such as hardware configuration and operating system information, are described within the simulation program with only a few of them being input parameters. The job mix is specified statistically with probability distributions read in, and the simulator generates jobs according to these distributions. The output of the program is in the form of response times, overhead times, swap times, etc. The simulation did reflect the behavior of the SDC computer fairly well.

Nielsen (13) extended the results of Scherr and of Fine and McIsaac in order to produce a more general time-sharing simulator. His simulation program successfully models the IBM System/360 Model 67, but it requires

some reprogramming to simulate most other systems.

Special simulation languages, such as GPSS and SIMSCRIPT, have been used to simulate various time-sharing systems, although these languages are not specifically designed to simulate only computer systems. There are simulation languages that have been designed specifically to model computer systems. IBM's CSS (Computer System Simulator) and LOMUSS (Lockheed's Multipurpose System Simulator) are two such languages.

The simulation efforts just described were undertaken in an attempt to simulate one particular time-sharing system. Ideally, a simulator would require only the input parameters to describe any system.

Unfortunately, no such simulator exists or is likely to exist for some time due to the differences in hardware and operating systems of the various time-sharing systems. In spite of its drawbacks, a simulation study appears to be the most promising means of analysis of a time-sharing system.

#### Selection of an Analysis Technique

To analyze only the paging structure of a time-sharing system, it may be possible to use strictly mathematical techniques. However, the object of this study is to investigate the behavior of the entire system with respect to changes in the paging structure. For this reason, it is necessary to select some analysis technique which can be used to model the entire time-sharing system. Since simulation offers the most promising results, it will be used.

The selection of a system to analyze also presents some interesting problems. Selecting a general time-sharing system, which in itself is very

difficult to define, raises the question of the validity of the simulation results with respect to any particular system. Also, the most successful simulations have been designed to simulate some particular system. Therefore, it appears that the most practical approach is to select some particular system which is representative of current time-sharing systems and to extend the results to other systems.

Ideally, the system selected should reflect the design used in most current time-sharing computer systems. It should be a well documented system with these documents readily available. And finally, there should be as many of these systems in use as possible, so that the behavior of the actual system is known. A system which meets all of these requirements is the IBM System/360 Model 67. Consequently, the Model 67 will be the system used.

Detailed descriptions of the Model 67 are given in papers by Gibson (5) and Comfort (1) as well as in an IBM publication (7). A brief description of this system is also given in the Appendix.

As a bonus for selecting the Model 67, the simulation by Nielsen, which has been shown to accurately reflect the behavior of this system, was available. A copy of this simulation program was obtained from Nielsen at the Stanford University Computation Center.

The simulation program finally used in this study was not the same as the one originally received. The original simulation apparently was designed to be as general as possible in order to simulate any paged, time-sharing system. To make the program simulate any particular system required some reprogramming. In order to simulate the structure desired for this study, a number of modifications had to be made to the original

simulation program. A copy of the final version used is available at the Iowa State University Computation Center Library.

#### A Description of the Simulation Program

In this section a brief description of some of the salient features of the simulation program is presented. For a more detailed description see the original work by Nielsen (13) or his two other papers (14) and (15) which also describe his original work.

#### Levels of simulation studies

An important consideration for any simulation is to determine what level of system activity is to be simulated. Four levels of simulation studies are given in Table 1.

Table 1. Levels of simulation studies

| Level | Size unit           | Time unit            |

|-------|---------------------|----------------------|

| 1 2   | job                 | seconds milliseconds |

| 3     | page<br>instruction | microseconds         |

| 4     | bit                 | nanoseconds          |

The first level is the one which is of most interest to the system's user. Although the user is interested in statistics in terms of jobs and seconds, these units are too large to produce a meaningful simulation.

The system designer is interested in simulations at the second level of

11

system study. The simulation by Nielsen is at this level with basic units of a page and 0.1 milliseconds. The third level is of some interest in a study of the paging structure, but any simulation of system behavior using this level's basic units becomes very long and time consuming. Fortunately, independent studies, both analytical and simulated, can be made at this level; and the results obtained can be used as inputs to the second level simulation with very good results. The fourth level is of no particular interest in a system study.

#### Representation of jobs

One of the most important aspects of the simulation program has to do with the methods used to represent jobs in the system. The validity of the simulation depends in many ways on the means used to represent jobs.

A common technique used to represent jobs in a system is to input to the simulation the distributions for the length of time a job executes in any page and the next page a job will reference. Since the characteristics of a job can change as the job progresses, it is desirable to have different distributions for the various stages of a job (e.g. compile, link-edit and execute).

Nielsen represents each section of a job as a sequence of page references and supervisor services appropriately spaced by execution times. Several of these sequences can be linked together and/or repeated in any desired manner to represent an entire job. For example, the syntax checking and table building phase of compiling a one hundred statement job could be handled by describing the sequence of operations for two statements and then repeating this sequence fifty times.

These sequences must be generated by the system's user for every desired job type in the system and are then input to the simulation program as master sequences. In this way the master sequences represent prototype jobs for each different job type. While the construction of these prototype jobs can be an extremely involved process, it is a once only operation for the simulation's user.

The simulation program uses the prototype jobs to construct the sequences for each job in the system. At the time that each of these sequences is constructed from a prototype, the simulation program determines according to appropriate random distributions the number of repetitions to be used, the terminal user's "think" time for each terminal interaction, the next master sequence to be used, etc. Because of the random nature used to construct each job sequence, no two jobs constructed from the same prototype are exactly the same. Two jobs of the same type will have the same characteristics, but they will not be carbon copies of one another.

A special job description language was developed to describe the job sequences. This language consists of a set of fourteen instruction types. Eight of these instruction types appear in both the master sequence and the specific job sequences. These instruction types determine the behavior of a job during its simulated execution time. They are used to specify the execution time before a particular operation is to occur and to control page accessing, terminal interactions, I/O operations, etc. The six other instruction types are used only in the master sequence. They are used to build the specific job sequences from the master sequence.

The description of the job representation presented here has been

necessarily brief. For a more detailed discussion, the reader is referred to the paper by Nielson (14) which has been almost entirely devoted to a description of the representation of jobs used in this simulation program.

#### <u>Implementation</u>

Nielsen implemented the simulation program in Fortran because he felt that there were no special simulation languages widely available. The source program consists of about 7000 statements organized into 31 subroutines each concerned with one particular aspect of the simulation. This modularity was used so that changes necessary to simulate other systems could be made as easily as possible.

In the simulation program one word is used to keep track of each page in the system whether it is a physical memory page or a virtual memory page. The word representing each page indicates the status of the page, the location of the page, and the task associated with the page. Queues in the system are represented by lists of words. To simulate a page on one of the queues in system, such as a page read queue, its word is attached to the list representing that queue.

Scheduling of events in the system is accomplished by the event calender queue. Entries are removed from this queue according to the earliest time of occurrence. A master clock is used to keep track of the system time in units of 0.1 milliseconds (i.e., the basic time unit). Statistics are gathered periodically by various routines during the simulation and are summarized at the end of the simulation to produce the output results.

#### Simulation inputs

Approximately 1500 data cards are used as inputs to the simulation program. The first set of data cards describe the monitor parameters. The monitor parameters include such things as the length of a time slice and the overhead times required to perform the many system functions. The next section is concerned with the equipment configuration. The names, quantities, capacities, transmission rates, rotational delays, seek times, etc. of the various devices in the system are given in this section. The next two sections contain the simulation run parameters and the data analysis parameters which are used to control the simulation and gather the statistics for the simulation's output. The terminal characteristics indicate which jobs are used in the system. Following this are the list of the prototype jobs and the list of instructions for the prototype jobs.

#### Simulation results

This section presents a description of the information which will be given in the table of results for each simulation run made for this study. It should be kept in mind that the simulation program produces much more information than can be included in the tables. Thus, the tables will present a concise listing of the most important simulation results.

Simulation times Two simulation times are given in the table of results. The first is the length of the initialization time in seconds. The simulation resets the statistics gathering procedure at the end of the initialization period. In this way, the problems of the startup and the initial transient of the model can be ignored. The second is the length of the simulation run in seconds after the statistics gathering

begins.

CPU data The percentages of CPU time used for execution, overhead, and idle are given in the tables of results. Execution time is the total amount of system time during which one task in the system is executing instructions. Since only one task can be executing at a time, all other tasks must be idle. Overhead time is the total amount of system time used by the monitor to perform such functions as I/O scheduling, interrupt handling, etc. While the system is performing overhead functions, all tasks are idle. Idle time is the total amount of system time during which no work is being done by the system (i.e., all tasks are idle and no overhead functions are taking place). It is important not to confuse system idle time and task idle time. The idle time given in the tables is system idle time. The distribution of execution, overhead, and idle times indicates how much useful work is being performed by the system.

Response times The response time is the time between two consecutive time slices for a task. It is an indication of the amount of time required by the system to respond to a request by a user at a terminal. The average response time in seconds is given in the table of results along with the range of response times. This range gives an indication of the best and the worst response times for the system.

Paging rates The average number of pages per second transmitted to and from (i.e., write and read, respectively) secondary storage is given in the tables. Also, the average number of pages per second retrieved from core queues before being replaced is given. These values indicate the amount of paging activity taking place in the system.

Queue data The average number of requests in the drum read and drum write queues is given for each simulation run. These values give some indication of the paging activity of the drums.

<u>Device utilization</u> The percentage of total time during which the drums and the nonpaging disks are used is given for each simulation run.

#### SELECTION OF A TEST CASE

In order to simulate the operation of any proposed time-sharing system, it is necessary to carefully define the equipment configuration and job mix that will be used as inputs to the simulation. The simulation studies cited in the previous chapter have shown that the performance of a time-sharing system is very sensitive to the details of this definition; therefore, some rational means must be employed in the selection of test cases which will be used to compare the performance of various systems.

Clearly, it is neither possible nor desirable to exhaustively test every combination. An arbitrary selection of a "typical" configuration and job mix leaves the not-so-small problem of defining just what is typical. There are, however, certain guidelines which can be used to make a reasonable selection.

The selection of an equipment configuration is based more on economic considerations than on equipment availability. Although system performance is very much dependent upon this configuration, there are fewer undefined variables involved than there are with the job mix selection; thus a reasonable equipment configuration can be readily determined.

Selection of a job mix to be used as a test case for a time-sharing system simulation is a different matter. What may be a "typical" job mix for one installation may be totally foreign to another. It soon becomes evident that there is no such thing as a general job mix. Any particular job mix selected must be justified solely on its applicability to the environment at hand. Some guidelines which can be used to make a selection of a job mix are:

- The job mix selected for the simulation should resemble a job mix found in the "real world". That is, the distribution of job types and lengths should be determined from a study of some actual installation.

- 2. The job mix should be stable with respect to order of jobs input to the simulation, starting time for each job, and length of the simulation runs. This means that after a suitable initialization period, the simulation process is time-stationary. Also, the simulation results should be insensitive to minor variations in the job mix.

- 3. More than one job mix may be needed to reflect the total system performance. Perhaps one mix is used for prime time operation (heavy conversational and light batch), and another mix is used for overnight operation (light conversational and heavy batch). Extremes in the job mixes may be one way to obtain the total performance.

After a stable job mix has been obtained, it is possible to use it with a number of simulations of proposed time-sharing systems and be reasonably certain that any variations in performance among the systems are significant. In other words, any variation is due to the system structure and not to the job mix.

#### Equipment Configuration

The equipment configuration selected for the test case will be made up of the hardware components available for the IBM System/360 Model 67. A study of an appropriate configuration for the Stanford University

Computation Center was used as a guide. The configuration selected is listed below.

- 1 GPU The processing unit is initially the 2067, the CPU of the 360/67. It has the computational power of the model 65 computer with the hardware capability of dynamic address relocation.

- 3 Core Storage Units (2365) Each unit has 262,144 bytes with a cycle time of 750 nanoseconds for an eight byte reference.

Three of these units provide 166 nonsystem pages (1 page = 4096 bytes) and 26 system pages for the Model 67.

- 2 Paging Drums (2301) Each drum has a capacity of 4,090,000 bytes or 900 pages (4½ pages per track). Transfer rate is 1,200,000 bytes per second and the rotational period is 17.2 milliseconds.

- 1 Disk (2314) There are 8 modules/disk, each with a separate access mechanism. Each disk has a total of 207,014,000 bytes and a transfer rate of 312,000 bytes per second.

The rotational period is 25 milliseconds, and the seek time is from 30 to 140 milliseconds.

- 4 Magnetic Tape Units These are nine track units with a transfer rate of 60,000 bytes/second.

- 3 Line Printers (1403) Each unit prints approximately 1100 lines/minute.

- 2 Card Reader Punches (2540) Each unit reads 1000 cards/minute and punches 300 cards/minute.

- 3 Selector Channels (2860) High speed devices (drums and disks) are attached to the selector channels.

- 1 Multiplexor Channel The slower I/O devices are attached to this channel.

- Transmission Control Units Each unit can control up to 31 remote terminals.

- Terminals As many terminals (teletypes) as required for the job load are attached to the system.

#### Job Mix Selection

This study involves the selection of the job mix (or mixes) to be used for the test cases. The guidelines previously presented will be followed, and both analytical and simulation methods will be employed to obtain a reasonable job mix.

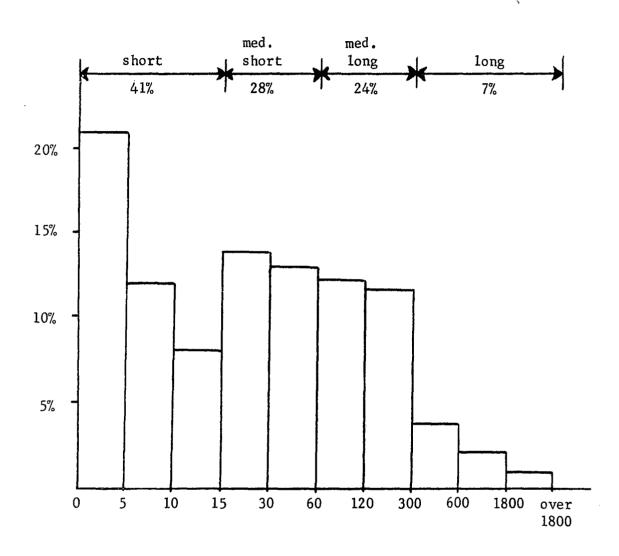

The first guideline is that the job mix should resemble one found in the "real world". The "real world" in this case will be the Iowa State University Computation Center. A distribution of job run times from June 15, 1967 to June 15, 1968 was obtained and is shown in Figure 1.

From this distribution it is possible to place the jobs according to run time into four main classifications:

| Short      | 0-15 sec     | 41% |

|------------|--------------|-----|

| Med. Short | 15-60 sec    | 28% |

| Med. Long  | 60-300 sec   | 24% |

| Long       | over 300 sec | 7%  |

Within each of these classes there would be a distribution according to job types. In general, conversational jobs would tend to be shorter

Run Time (Seconds)

Figure 1. Distribution of job run times

than batch jobs. The dismistribution of run times for conversational jobs would tend to be skewed to toward the shorter run times. The batch jobs would tend to be skewed to toward the longer run times with respect to the total job mix.

#### Job list for simulation

Stanford University of developed a list of 35 job types for the simulation along with the appropriate instruction list for each job type. This list, which required threaree man-months to assemble, reflects the general types of jobs likely to be found in a time sharing system. No claim is made that a job type repropresents the exact behavior of any real job. However, the job types do harhave the same characteristics of a real job (e.g., a list processing job willil do a lot of paging).

The job mix is obtained by selecting job types from this list. Any job type on the list may be used as many times as needed to form the desired distribution. In In addition the starting time and the waiting time before a completed job representation itself must be specified for each job.

The list of job type pes along with their priorities and run time classifications is given in Tabsable 2.

Simulation Series I [I was designed to aid in the selection of a job mix and to determine the se test cases which could be used to compare the performance of later seringines with that of the Model 67 as simulated in this series. The results of this series of simulations are given in Table 3.

#### Test mix 1 - totally corponversational

In order to eliminatuate as many variables as possible in the selection of a stable job mix, the he first test mix is totally conversational.

Table 2. Simulation job list characteristics

| Job | Description            | Priority <sup>a</sup> | Run Time<br>Classification |

|-----|------------------------|-----------------------|----------------------------|

| 1   | 1000 statement conv.   | 2                     | medium short               |

| 2   | 1000 statement conv.   | 2                     | medium short               |

| 3   | 1000 statement conv    | 2                     | medium short               |

| 4   | 1000 statement batch   | 3                     | medium short               |

| 5   | 1000 statement batch   | 3                     | medium short               |

| 6   | 1000 statement batch   | 3                     | medium short               |

| 7   | 150 statement conv.    | 2                     | short                      |

| 8   | 150 statement conv.    | 2                     | short                      |

| 9   | 150 statement conv.    | 2                     | short                      |

| 10  | 150 statement batch    | 3                     | short                      |

| 11  | 150 statement batch    | 3                     | short                      |

| 12  | 150 statement batch    | 3                     | short                      |

| 13  | 50 statement conv.     | 2                     | short                      |

| 14  | 50 statement conv.     | 2                     | short                      |

| 15  | 50 statement conv.     | 2                     | short                      |

| 16  | file maintenance       | 3                     | medium long                |

| 17  | desk calculator        | · 2                   | short                      |

| 18  | game                   | 2                     | medium short               |

| 19  | heavy cmpt. conv.      | 2                     | medium long                |

| 20  | heavy cmpt. batch      | 3                     | medium long                |

| 21  | tape to file           | 1                     | medium short               |

| 22  | file to tape           | 1                     | medium short               |

| 23  | disk to print          | 1                     | medium long                |

| 24  | card to disk           | 1                     | medium long                |

| 25  | list proc. med. conv.  | 2                     | medium long                |

| 26  | list proc. med. batch  | 3                     | medium long                |

| 27  | list proc. large conv. | 2                     | long                       |

| 28  | list proc. large batch | 3                     | long                       |

| 29  | prog. ckout system     | 2                     | short                      |

| 30  | production med. conv.  | 2                     | medium long                |

| 31  | production med. batch  | 3                     | medium long                |

| 32  | production large conv. | 2                     | long                       |

| 33  | production large batch | 3                     | long                       |

| 34  | short execute          | 2                     | medium short               |

| 35  | never finish           | 2                     | long                       |

<sup>&</sup>lt;sup>a</sup>Priority level 1 - I/O jobs Priority level 2 - Conversational jobs Priority level 3 - Batch jobs

Table 3. Results of Simulation Series I

| Run                               | la             | 1b             | 1c             | 1d             | le             | 2a             | 2ъ             |  |

|-----------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

| Initialization time               | 30             | 30             | 30             | 60             | 60             | 30             | 60             |  |

| Run_time                          | 180            | 180            | 180            | 180            | 300            | 180            | 180            |  |

| CPU data<br>Execution             | 33.6%          | 33.7%          | 33.8%          | 34.8%          | 34.8%          | 40.8%          | 38.9%          |  |

| Overhead<br>Idle                  | 33.2%<br>33.2% | 32.3%<br>34.0% | 32.7%<br>33.4% | 33.1%<br>32.1% | 33.2%<br>32.0% | 33.2%<br>26.0% | 33.7%<br>27.4% |  |

| Response time                     |                |                |                |                |                |                |                |  |

| Average<br>Range                  | 1.57<br>1-3    | 1.57<br>1-3    | 1.57<br>1-3    | 1.64<br>1-3    | 1.64<br>1-3    | 3.10<br>1-6    | 3.11<br>1-6    |  |

| Paging rates                      |                |                |                |                |                |                |                |  |

| Read                              | 27             | 26             | 27             | 28             | 28             | 30             | 32             |  |

| Write                             | 52             | 48             | 48             | 50             | 49             | 36             | 37             |  |

| Pages retrieved                   | 43             | 38             | 40             | 41             | 40             | 17             | 17             |  |

| Drum queue data                   |                |                |                |                |                |                |                |  |

| Read - average<br>Write - average | 2.0<br>1.8     | 2.0<br>1.9     | 2.0<br>1.8     | 2.0<br>1.9     | 2.1<br>1.8     | 2.2<br>1.7     | 2.2<br>1.6     |  |

| Device utilization<br>Drums       | 15%            | 13-15%         | 12-16%         | 12-17%         | 13-16%         | 12-13%         | 12-13%         |  |

| Nonpaging disks                   | 2-38%          | 2-37%          | 2-41%          | 1-43%          | 1-42%          | 3-41%          | 2-44%          |  |

Table 3 (Continued)

| Run                                                         | 2c                      | 3a                    | 3ъ                    | 3с                    | 4                       |

|-------------------------------------------------------------|-------------------------|-----------------------|-----------------------|-----------------------|-------------------------|

| Initialization time                                         | 60                      | 30                    | 60                    | 60                    | 60                      |

| Run time                                                    | 300                     | 180                   | 180                   | 300                   | 180                     |

| CPU data<br>Execution<br>Overhead<br>Idle                   | 40.1%<br>33.7%<br>26.2% | 31.8%                 |                       | 31.8%                 | 42.2%<br>41.1%<br>16.7% |

| Response time<br>Average<br>Range                           | 3.09<br>1-6             | 3.82<br>3-5           | 3.82<br>3-5           | 3.81<br>3-5           | 3.04<br>2-5             |

| Paging rates Read Write                                     | 32<br>37                | 22<br>29              | 23<br>29              | 22<br>28              | 60<br>56                |

| Pages retrieved  Drum queue data  Read - average            | 2.2                     |                       |                       | 15<br>1.8             | 13<br>3.4               |

| Write - average  Device utilization  Drums  Nonpaging disks | 1.6<br>13%<br>2-43%     | 1.6<br>9-10%<br>2-33% | 1.6<br>9-10%<br>1-35% | 1.5<br>9-10%<br>1-35% | 22%<br>1-45%            |

After a stable, conversational job mix has been determined, background jobs will be added to produce a combined mix.

Twenty five jobs are used with job types which were selected to fit the distribution previously determined. Since all jobs are conversational in nature, the distribution was skewed slightly toward the short jobs.

Simulation runs (Series I - Run 1) were used to determine the stability of the job mix with respect to order of jobs input to the simulation, starting time for each job, and length of the simulation runs.

Run la was made with the order of input jobs as given above, and all jobs started at the same time. Run lb was made with the order of the jobs completely reversed, all jobs starting at the same time; and Run lc was made with different starting times for the various jobs. A comparison of the results for these runs shows very little variation. Note that due to the random methods used to produce jobs in the simulation, the job mixes produced by re-ordering the input sequence are not identical. The job types are the same, but the individual jobs are not necessarily the same. For this reason a slight amount of variation in the results should be expected.

Increasing the initialization period (Run 1d) only produces a slight variation in the results. An initialization period of 60 seconds (Run 1d) appears to be adequate to produce consistent results.

A longer run (Run le) shows virtually no change in results with respect to the shorter run (Run ld). Therefore, Run ld was selected as the representative run for this test mix.

These simulations show that the job mix selected is stable. The results of Run ld indicate that for this mix the CPU time is just about

evenly distributed between execution time, overhead time and idle time; and the average response time is 1.6 seconds.

#### Test mix 2 - background jobs added

Having determined that the conversational job mix selected is stable, it was then possible to add some batch jobs—to make a combined mix. This combined job mix now fits the desired "real world" distribution. The distribution is shown in Figure 2.

The performance results for this heavy conversational-light batch job mix were given by Simulation Series I - Run 2.

Runs 2a, 2b, and 2c were made with different values of initialization periods and run times. The only difference in the results of these three runs is a small variation in CPU utilization times. Run 2b was selected as the representative run for this job mix.

A comparison of the results of Runs 1 and 2 shows that adding some batch jobs to the conversational mix shifts about 4-5% of the total CPU time from idle time to execution time, while the overhead remains about the same. The response time increased from 1.6 seconds to 3.1 seconds. This is due to the fact that the operational cycle time (OCT) for the system is set to 3 seconds. Also note that the total paging activity has been reduced by adding the batch jobs.

#### <u>Test mix 3 — heavy batch jobs</u>

In order to obtain the results for a light conversational — heavy batch job mix, a third test mix was developed. Once again the "real-world" distribution was used to produce an appropriate mix.

|                |    | ort                           |    |       |                            | l. sh | ort | med. long |     |    |          |          |    |    | 1ong     |    |    |    |  |

|----------------|----|-------------------------------|----|-------|----------------------------|-------|-----|-----------|-----|----|----------|----------|----|----|----------|----|----|----|--|

|                | 4  | 1%                            |    |       |                            | 28%   |     |           | 24% |    |          |          |    |    |          | 7  | 7% |    |  |

|                |    | X<br>X                        |    |       | 0<br>X<br>X                |       |     |           |     |    |          |          |    |    |          |    |    |    |  |

| X              |    | X                             |    |       | X                          |       |     |           |     |    |          |          |    |    |          |    |    |    |  |

| X<br>X         |    | X<br>X                        |    |       | X<br>X                     |       |     | X         |     | X  |          | Х        |    |    |          |    |    |    |  |

| X              | X  | X                             | X  |       | X                          | Х     |     | ı X       | 0   | X  |          | X        |    |    | 1 0      |    | 0  |    |  |

|                | •• |                               | •• |       |                            |       |     |           |     |    |          |          |    |    |          |    |    |    |  |

| 13<br>14<br>15 | 17 | 7<br>8<br>9<br>10<br>11<br>12 | 29 | 21 22 | 1<br>2<br>3<br>4<br>5<br>6 | 34    | 18  | 25        | 16  | 19 | 23<br>24 | 30<br>31 | 26 | 20 | 27<br>28 | 32 | 33 | 35 |  |

The 35 job types (ordered by run time)

X = Conv. jobs

0 = Batch jobs

Figure 2. Job mix distribution for test mix 2

Twenty batch jobs and nine conversational jobs are used to make this mix. The distribution of these jobs is shown in Figure 3.

Simulation Series I — Run 3 was used to provide the performance results for the light conversational — heavy batch job mix.

Runs 3a, 3b, and 3c were made with different values of initialization periods and run times. No significant variation exists between the three runs; so Run 3b was selected as the representative run for this job mix.

The results show that execution time has increased significantly, idle time has decreased by the same amount, and overhead time is about the same as for Runs 1 and 2. Average response time is up to 3.8 seconds, and the total paging activity is further reduced.

#### Validity of test cases

The test mixes developed were designed to represent the types of jobs found in a time-sharing system and to fit the run time distribution of an actual system. One question still remains: How well do the test mixes reflect the paging behavior of jobs found in a time-sharing environment?

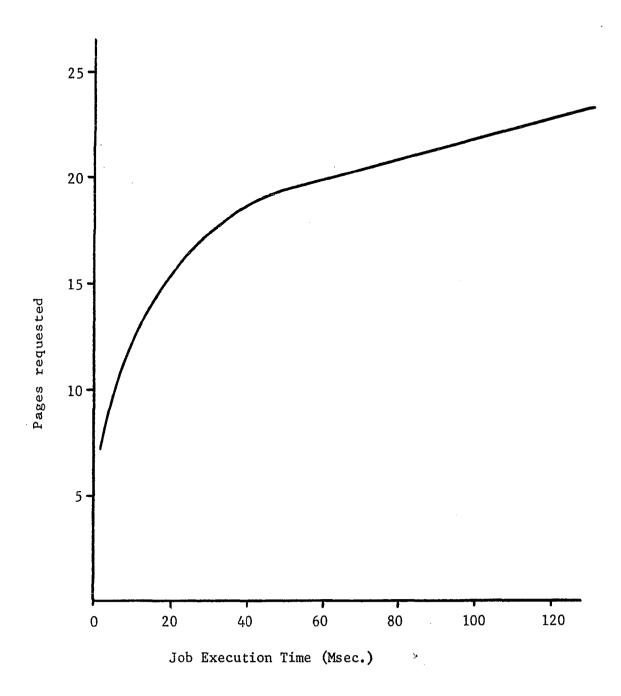

System Development Corporation (SDC) investigated the paging behavior of several programs that might be typical in a time-sharing system. The results of this investigation are presented in a paper by Fine et al. (3). Figure 4 shows the number of pages demanded by a job as a function of the job execute time. The assumption is made that the job starts with no pages and each page is brought in on demand. The demand paging rate is very high at the beginning of the time slice, but it decreases after a sufficient number of pages has been made available. During a 100 millisecond time slice (the same length used for the simulation runs) a job

|    | sho | rt | med. short |     |    |     |    |    | m   | ed. | long | long |    |    |    |    |    |    |  |

|----|-----|----|------------|-----|----|-----|----|----|-----|-----|------|------|----|----|----|----|----|----|--|

|    | 41  | %  |            | 28% |    |     |    |    | 24% |     |      |      |    |    | 7% |    |    |    |  |

|    |     |    |            |     |    |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     |    |            |     |    |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 0  |            |     |    |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 0  |            |     | 0  |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 0  |            |     | 0  |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 0  |            | 0   |    |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 0  |            |     | 0  |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 0  |            |     | ٠0 |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

| X  |     | Х  |            |     | 0  |     |    |    |     |     |      | 0    |    |    |    |    |    |    |  |

| Х  |     | X  |            |     | X  |     |    |    |     |     |      | 0    |    | 0  |    |    |    |    |  |

| X  |     | X  |            |     | X  |     |    |    | 0   |     |      | X    | 0  | 0  | 0  |    | 0  |    |  |

| 13 | 17  | 7  | 29         | 21  | 1  | 34  | 18 | 25 | 16  | 19  | 23   | 30   | 26 | 20 | 27 | 32 | 33 | 35 |  |

| 14 |     | 8  | _,         | 22  | 2  | - ' |    | _  |     |     | 24   | 31   |    |    | 28 |    |    |    |  |

| 15 |     | 9  |            |     | 3  |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 10 |            |     | 4  |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 11 |            |     | 5  |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

|    |     | 12 |            |     | 6  |     |    |    |     |     |      |      |    |    |    |    |    |    |  |

The 35 job types (ordered by run time)

X = conv. jobs

0 = batch jobs

Figure 3. Job mix distribution for test mix 3

Figure 4. Paging behavior of time-sharing jobs

references approximately 22 pages. This means that during its execution time, a job requests pages at the average rate of about 220 pages per second.

The simulation program produces the total number of pages requested by the job mix for each run. The results of the simulation runs show that during their execution time, job mixes 1, 2, and 3 request pages at the average rates of 216, 154, and 90 pages per second, respectively. Thus, job mix 1 has essentially the same demand paging rate as the jobs studied by SDC. Job mixes 2 and 3 have somewhat lower rates because of their background jobs which require less paging.

In order to obtain the total performance of the time-sharing systems being studied, all three job mixes will be used. These test mixes were designed to represent extremes in the job load. If only one mix had to be selected, it would most likely be somewhere between job mixes 2 and 3. A single job mix which can be used to evaluate the total system performance is difficult to define. For this reason extremes are used.

Also note that none of the job mixes contain any bulk I/O jobs (e.g., card to disk, disk to print, etc.). The simulation runs are so short that any bulk I/O jobs tend to dominate the system activity, and the simulation results reflect this fact. Since it is the paging structure that is being investigated, the decision to eliminate the bulk I/O jobs is justifiable. As a consequence of this decision, the tape units, the card reader-punches, and the line printers are not used during the simulation runs.

# Comparison of results

Since the same equipment configuration and job length distribution were used in each run, a comparison of the results obtained by varying job types can be made. Some generalizations that can be drawn from a comparison of Runs 1d, 2b, and 3b are given below.

<u>CPU utilization</u> As the job types progress from totally conversational to totally batch, the system idle time is exchanged for execution time with the overhead time remaining fairly constant. This is as expected since the purpose of having background jobs is to use the idle time.

Response time The price paid for reducing the idle time by adding background jobs is an increase in response time. The response time is lowest with all conversation jobs. Addition of a few background jobs causes the response time to rise sharply and then level off, rising only slightly, as more background jobs are added. The value at which this limiting action takes place is set by the operational cycle time (OCT) of the system. For this configuration the OCT is equal to 3 seconds. Increasing the OCT would give more CPU cycles to the background jobs, while decreasing it would give less.

Paging rate As the percentage of batch jobs increases, the paging rate decreases. Batch jobs tend to have longer run times and execute longer without interruption than do conversational jobs. Therefore, the paging rate (pages per second) is generally less for a batch job.

# Special test mix - heavy paging

The performance results with job mix 1 show that the system is idle a good deal of the time. This, together with the fact that a large number

of pages are retrieved from the core allocation queues, indicates that the system can handle a heavier job load. An additional simulation run (Run 4) was made with job mix 1 doubled in size to provide the system with 50 jobs having the same characteristics as mix 1.

Comparing the results of Run 4 with those of Run 1d shows that much of the idle time has been reduced, the response time has doubled, and the paging rate has been increased. This double job mix will be used as a test mix when runs with heavy paging requirements are desired.

#### PAGING STRUCTURE OF A TIME-SHARING COMPUTER SYSTEM

The results in the previous chapter indicate that the CPU is either idle or is performing overhead functions much of the time. Neither of these is directly beneficial to the progress of a particular user's problem. This study will investigate some of the causes of these high idle and overhead times, and methods to improve the performance of the system will be proposed.

The paging structure is primarily responsible for the poor system performance. To demonstrate this, it will be necessary to examine the paging structure philosophy used in many current time-sharing computer systems of which the IBM System/360 Model 67 is a representative example.

# Demand Paging

A fixed-sized page is brought into main memory only after some location in that page has been referenced. This concept is known as demand paging. After a task has referenced a new page, that task is placed in a page wait state, and none of its pages in main memory can be used until the referenced page is brought in. During this wait, control is given to another user, assuming that there is another user. In this way page fetching is overlapped with processing. It is possible, and indeed quite probable, that all tasks occupying main memory are in a page wait state. This condition results in CPU idle time. In addition heavy paging demands can also cause congestion at the paging devices which may result in poor user response.

In an attempt to minimize some of the problems just described, alternatives to demand paging have been suggested. The concept of

affinity paging involves bringing into main memory groups of pages which have an affinity for each other. Whenever a single page is referenced, the monitor is to recognize that certain other pages are likely to be required and brings in these pages along with the referenced page. Of course, this concept assumes the ability of the monitor to recognize page affinities. To provide this ability, the user would most likely have to supply these page relationships or else organize programs so that they might be easily segmented. This approach of fitting the jobs to the system instead of vice versa does not appear to be realistic and for this has not been universally accepted. Because of a lack of a suitable alternative, current time-sharing philosophy seems to be firmly committed to the demand paging concept.

Paging devices must be able to deliver pages at the rate required by the system. Three types of paging devices currently used in time-sharing computer systems are described below.

# Paging disks

The configuration of the Model 67 allows disks to be used in conjunction with a drum as the paging devices. The slower disks are used primarily as back-up devices for the drum. In his original simulations Nielson (13) demonstrated that the disks seriously degraded the system performance because of their inability to deliver pages at the required rate and suggested that the paging disks be replaced by an additional drum. For this reason no paging disks are included in the equipment configuration used to develop the test cases.

# Paging drums

Drums are the most common paging devices used in current time-sharing systems. Some investigators have suggested that paging drums are not able to deliver pages at the required rate and should not be used when heavy paging demands are involved. A detailed discussion on paging drums is deferred until a later section.

# Large capacity core storage (LCS)

LCS provides the most rapid (and most expensive) means of delivering pages to requesting tasks. There are two ways in which LCS can be used. The first is to use LCS in a manner analogous to the use of paging drums. Whenever a page is requested by some task, that page is located in LCS and brought into main memory. The second way is to execute directly from the slower speed LCS, thereby eliminating a page transfer. This second method can be used very effectively if the number of references to a page is small or if time-sharing is only a small part of the total system function. It has been suggested by Lauer (10) that a combination of these two methods can be used. That is, when a large number of references is to be made to a page, that page should be transferred from LCS to main storage; if the number of page references is small, LCS can be accessed directly. Unfortunately, there is presently no way for the system to determine before the fact how many references will be made to a page, and because of this, the combination method does not seem to be a practical solution.

## Drum Paging Structure

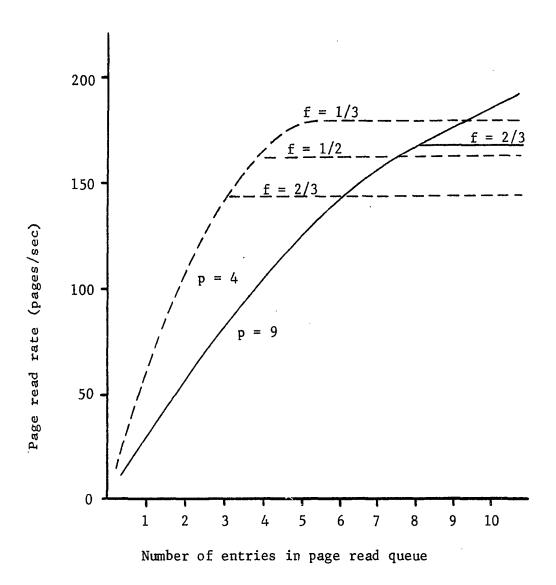

Lauer also analyzed the drum paging structure used for a time-sharing system. The drum that he considered has one read-write head per track,

but only one head can be connected to the channel at any one time. There are p pages per track with sufficient space between pages to permit head switching. Thus, on one drum revolution p pages may be read and/or written. This is equivalent to one head passing p slots per revolution. The maximum rate at which pages can be transferred to or from a drum is  $\frac{p}{T}$  pages per second where T is the time required for one drum revolution. Page writes are necessary for those pages which have been changed during a task's time slice and now must be paged out to make room for a subsequent task's pages. If f is the probability that a page must be written out, then  $\frac{p}{(1+f)}$  T pages per second is the maximum average rate at which pages can be read from the drum.

Only one page can be read from a slot per revolution. A slot conflict occurs when more than one page is requested from the same slot at the same time. Under this condition only one request can be serviced on the current revolution; the rest will have to be delayed until they can be serviced on some future revolutions of the drum. Because of slot conflicts, the maximum average rate at which pages can be read from a drum can only be approached. Page writes do not generate slot conflicts. When the channel program is set up to control the drum operation during the next revolution, the monitor first schedules as many read requests as possible and then schedules page writes for the unused slots.

Lauer states that the average rate at which pages can be read is given by the results of the probability exercise known as the Urn-model Occupancy problem. Figure 5 shows the average page read rate as a function of f and k, the number of requests in the page read queue. The case p = 9, T = 34.4 milliseconds is the one used for the test cases. For this

Figure 5. Average page read rate

configuration  $4\frac{1}{2}$  pages are placed on each track so that 9 pages can be referenced during a double drum revolution. The case p = 4, T = 17.2 milliseconds is the same drum reorganized so that 4 pages can be referenced during each drum revolution.

From the figure it appears that a high page read rate is only possible with a long read queue. Each entry in the read queue represents one task which cannot continue executing because it has been placed in a page-wait state. Lauer has concluded that the paging device must deliver pages at the rate requested by the job mix in order to minimize the CPU idle time. Therefore, if drums are used, long read queues must result and a large amount of main storage must be available to support the large number of tasks in a page-wait state. He has further concluded that drums are not well suited as paging devices and should be replaced by LCS.

It was previously shown that job mix 1 requests pages at an average rate of about 216 pages per second. If the drums must deliver pages at this rate, the conclusions drawn by Lauer may be correct. However, it can be demonstrated that the actual rate at which the drums must deliver pages is considerably less.

There are two major reasons why the rate at which the drums must deliver pages is less than the rate requested by the job mix. First, and most important, heavy page requests are only generated during a task's execution time. No pages are requested during system idle time, and only a few, if any, are likely to be requested by the system during overhead time. Therefore, the average rate at which pages are requested is 216 pages per second only if the system execution time is 100% of the CPU time,

a situation which is highly unlikely to even be approached.

The second reason is that not all page requests produce page reads. A page request can be satisfied in one of four ways. In addition to being read from a paging device, the requested page may have been read during a previous time slice and is still available to be retrieved; it may be read from an I/O device; or finally it may be a shared page which is in main memory being used by some other task.

As an example, consider Simulation Series I — Run 4. The results of this simulation show that the system execution time only accounts for 42% of the total CPU time. This means that the tasks are generating page requests only 42% of the time or at an average rate of only 90 pages per second. Of the 90 pages per second requested, an average of 60 pages per second are read, 13 pages per second are retrieved, and the remaining 17 pages per second are either shared pages or are obtained from I/O devices. While it is recognized that the requested rate may at times exceed the rate at which the drums can deliver pages, the important point is that the drums can keep up with the requested rate by delivering an average of only 60 pages per second and not the 216 pages per second as originally assumed. For the average read queue length of 3.4 requests, Figure 5 indicates that each drum can easily deliver 60 pages per second.

The size of the read queue also indicates the number of tasks currently in a page-wait state. For the example cited the average number of tasks in main memory at any one time is approximately six. The average size of the read queue indicates that about half of these tasks are in a page-wait state; the rest are ready to execute. The fact that the drums

only deliver pages at an average rate of 60 pages per second has not resulted in excessive system idle time caused by many tasks waiting for page reads.

There is an explanation for the discrepancies between the results given in Lauer's paper and the results of this study. Lauer has assumed that the worst case situation is the normal mode of operation in a time-sharing system. The results presented here indicate that his assumption is not valid.

#### IMPROVEMENT OF SYSTEM PERFORMANCE

An effective way to improve the performance of the time-sharing computer system is to increase the amount of useful work performed by the system. To accomplish this, it is necessary to increase the fraction of time devoted to CPU execution by reducing the unproductive system time. Because service to the user is of paramount importance in any time-sharing system, care must be taken to insure that a reasonable response time is provided. In the following sections, modifications to the paging structure of the drum-oriented system will be proposed in an attempt to achieve the goal of improved hardware efficiency. The detailed evaluation of all of the proposed changes to the paging structure is postponed until the next chapter.

There are two main causes of CPU idle time in a time-sharing system.

One is a lack of work for the system to perform, and the other is the inability to deliver pages to waiting tasks. Idle time caused by a lack of work can be reduced by providing background jobs which execute when no other work is available and which relinquish control when a higher priority job (e.g., conversational job) is ready. The results of Simulation Series I have shown how the addition of background jobs has significantly reduced system idle time.

The second cause is not so easy to resolve. CPU idle time results when all tasks in main memory are in a waiting condition. If the rate at which the drums can deliver pages could be increased, the average number of tasks in a page-wait state, along with system idle time, should be reduced. Figure 5 indicates that if the drums are reorganized with 4

pages per track rather than the original 4½ pages per track, the rate at which pages can be delivered is greatly increased. The cost of reorganizing the drums is an 11% reduction in drum capacity.

Simulation Series II - Runs 1a, 2a, 3a, and 4a were used to simulate the original system with the reorganized drums. The results are given in Table 4. A comparison of these results with those of the original system (Series I - Runs 1d, 2b, 3b, and 4) shows that, as predicted, the system idle time and the size of the drum read queues have been reduced. It is interesting to note that the percentage of CPU time used for execution is practically unchanged. Overhead time has increased because of the additional number of interrupts necessary to schedule the drums for every single revolution rather than for every double revolution as was originally the case. Even though the reorganized drums are capable of delivering pages at nearly twice their original rate, the average number of pages read per second is essentially the same. Thus, it appears that this reduction in system idle time has not significantly improved the performance of the system. It should also be quite clear that even if all of the CPU idle time could be eliminated, a considerable amount of time is still devoted to overhead. While it is important to be able to reduce the system idle time, something must be done about overhead time before any major improvement in performance will be achieved.

Overhead times cannot be reduced in the same manner as were system idle times. Overhead is the amount of CPU time needed by the monitor to perform such functions as interrupt handling and I/O scheduling and is, therefore, inherent in any system. The paging structure in a time-sharing system is chiefly responsible for the high overhead times. The remainder

Table 4. Results of Simulation Series II

}

| Run                                            | la                      | 1b              | 1c                      | 2a                      | 2b                      | 2c              |

|------------------------------------------------|-------------------------|-----------------|-------------------------|-------------------------|-------------------------|-----------------|

| Initialization time                            | 60                      | 60              | 60                      | 60                      | 60                      | 60              |

| Run time                                       | 180                     | 180             | 180                     | 180                     | 180                     | 180             |

| CPU data Execution Overhead Idle               | 37.4%<br>43.2%<br>19.4% | 35.9%           | 41.2%<br>31.5%<br>27.3% | 39.1%<br>42.4%<br>18.5% | 46.1%<br>34.7%<br>19.2% |                 |

| Response time<br>Average<br>Range              | 1.55<br>1-3             | 1.43<br>1-3     | 1.39<br>1-3             | 2.92<br>1-5             | 2.85<br>1-5             | 2.91<br>1-5     |

| Paging rates<br>Read<br>Write                  | 31<br>56                | 29<br>57        | 27<br>61                | 33<br>39                | 34<br>40                | 33<br>39        |

| Pages retrieved  Drum queue data               | 47                      | 52              | 58                      | 20                      | 21                      | 20              |

| Read - average Write - average                 | 1.7<br>1.9              | 1.7<br>2.0      | 1.5<br>2.1              | 1.8<br>1.8              | 1.7<br>1.9              | 1.8<br>1.8      |

| Device utilization<br>Drums<br>Nonpaging disks | · <del>-</del>          | 17-21%<br>1-48% | 18-20%<br>1-49%         | 15-17%<br>2-41%         | 16-17%<br>2-38%         | 14-18%<br>2-42% |

Table 4 (Continued)

| Run                                                  | 3a                     | 3ъ                     | 3c              | 4a 🕚            | 4Ъ                      | 4c              |

|------------------------------------------------------|------------------------|------------------------|-----------------|-----------------|-------------------------|-----------------|

| Initialization time                                  | 60                     | 60                     | 60              | 60              | 60                      | 60              |

| Run time                                             | 180                    | 180                    | 180             | 180             | 180                     | 180             |

| CPU data Execution Overhead Idle                     | 56.5%<br>40.5%<br>3.0% | 65.0%<br>31.3%<br>3.7% | 26.9%           |                 | 43.9%<br>43.9%<br>12.2% |                 |

| Response time<br>Average<br>Range                    | 3.54<br>3-5            | 3.55<br>3-5            | 3.56<br>3-5     | 3.03<br>2-5     | 2.88<br>2-5             | 2.75<br>2-5     |

| Paging rates<br>Read<br>Write                        | 23<br>31               | 23<br>32               | 24<br>31        | 59<br>56        | 61<br>60                | 64<br>62        |

| Pages retrieved                                      | 23                     | 23                     | 21              | 17              | 21                      | 19              |

| Drum queue data<br>Read - average<br>Write - average | 1.5<br>1.6             | 1.4<br>1.9             | 1.6<br>2.0      | 2.2<br>2.1      | 2.4<br>2.7              | 2.4             |

| Device utilization<br>Drums<br>Nonpaging disks       | 11-13%<br>1-38%        | 11-13%<br>1-29%        | 11-13%<br>1-32% | 25-26%<br>1-45% | 26-27%<br>1-47%         | 27-28%<br>1-50% |

of this chapter will examine some of the causes of high overhead and will evaluate changes to the paging structure which are proposed to reduce overhead times.

فمررسه

## Scheduling of the Paging Drums

Each drum operates independently under the control of its own channel program. A new channel program must be set up for each drum revolution. To accomplish this, the CPU is interrupted before the start of the next revolution, and pages are scheduled to be read or written during the next revolution. Another interrupt at the start of the revolution gives the channel program control of the drum. This operation is performed for every single revolution, whether or not there are pages transferred to or from the drum. Each drum revolves approximately 60 times a second, causing about 120 channel programs to be set up per second for the two drums. This amounts to a great deal of unnecessary overhead time if pages are not transferred during every revolution.

Previous results have demonstrated that the drums are not busy at all times. This is especially true for the job mixes which have very low paging requirements. For this reason the decision was made to eliminate some of these unnecessary interrupts in order to reduce the overhead time. The procedure used is particularly simple. When no pages are being read or written on the current revolution, the next regularly scheduled drum interrupt is skipped. If the drums are used during every revolution, then this procedure has no effect. On the other hand, when very little paging activity is involved, up to half of the originally scheduled interrupts are climinated.

The fact that no pages are being transferred on the current revolution indicates that no pages are currently pending in a read or write queue. Any request entering one of these queues after the decision has been made to skip the next revolution will be delayed longer than usual. This may result in a slight increase in the size of the read or write queues. The overall system performance, however, should be increased due to the decrease in overhead time.

Simulation Series II — Runs 1b, 2b, 3b, and 4b were used to simulate the system with the reorganized drums and the drum scheduling procedure just described. The results of this set of runs indicate a definite improvement in performance. This can be seen by comparing the simulation results with those of Runs 1a, 2a, 3a, and 4a. Overhead has been substantially reduced causing an improvement in both execution and reponse times. The drum scheduling procedure appears to be a very beneficial addition to the system.

# Multiple Sets of Registers

The drum scheduling procedure has reduced the overhead by eliminating some of the interrupts required by the system. This procedure is most effective when the drums are not being used to their fullest extent but has little or no effect when high paging rates are involved. Certainly it is equally important, if not more so, to improve the performance of the system with high paging rates. The previous discussion and results indicate that there are gains to be made by using a more efficient interrupt structure.

An efficient interrupt structure is an especially important asset for

a real-time computer system. The Scientific Data Systems (SDS) SIGMA 7 time-sharing computer system was designed primarily to solve the problem of achieving true real-time response. A set of 16 general registers is provided in the system. As an option, multiple sets of these registers can be included. In this way, when an interrupt occurs, it is not necessary to store the contents of the set of registers in order to preserve the condition of the system before the interrupt. Instead, a new set of registers can be used to service the interrupt. The need to restore the registers at the end of the interrupt to their condition prior to the interrupt has also been eliminated. Hence, this technique saves the time needed to store and load the set of general registers for every interrupt. The only time required is about 6 microseconds to switch control from one set of registers to another. A detailed description of the design features for the SIGMA 7 is presented in a paper by Mendelson and England (12).

This idea of adding sets of general registers to increase the efficiency of the interrupt structure should greatly improve the system performance. A set of simulations was designed to determine how much of a gain could be achieved with the addition of five sets of register (one set for each of the five classes of interrupts in the System/360). The results of Simulation Series II — Runs 1c, 2c, 3c, and 4c show that in all cases over 4% of the total CPU time has been removed from the overhead time and has been distributed between execution and idle times.

The results in this and the previous section indicate that much can be gained through modification of the interrupt structure. A detailed evaluation of these performance improvements will be made after all other changes to the paging structure have been presented.

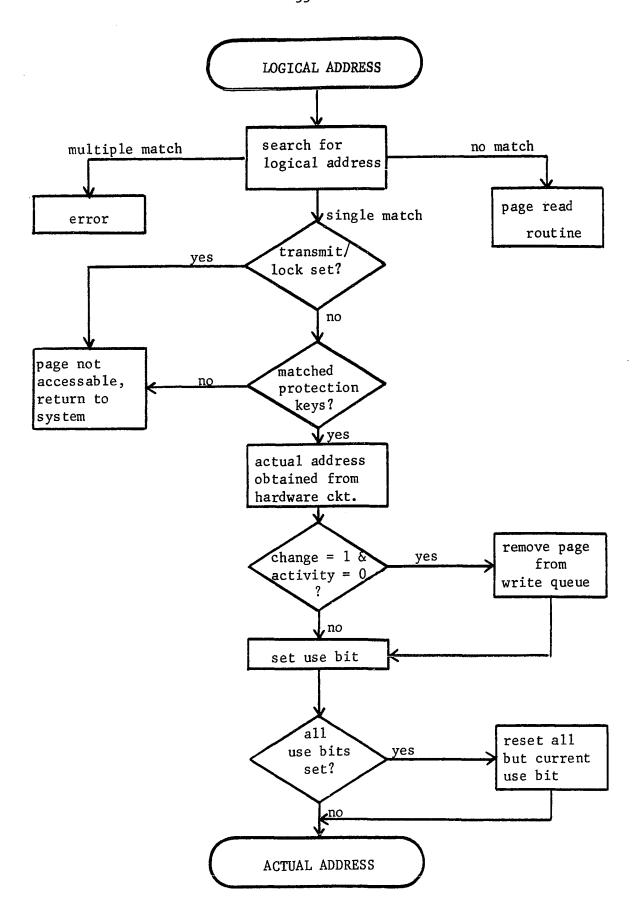

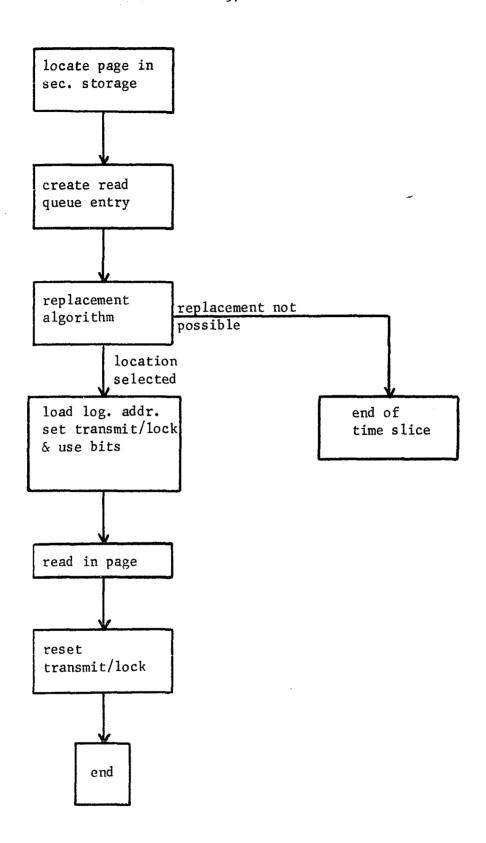

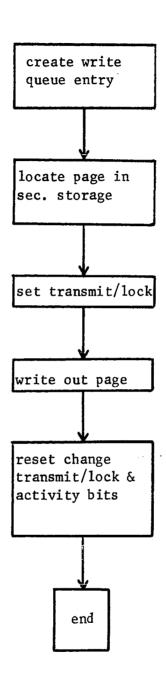

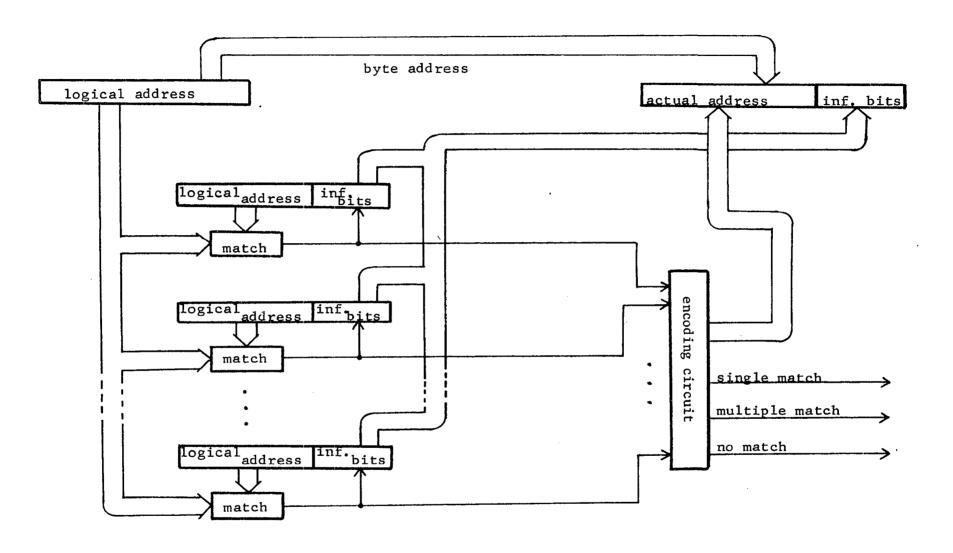

## Hardware Paging Structure